| [1] |

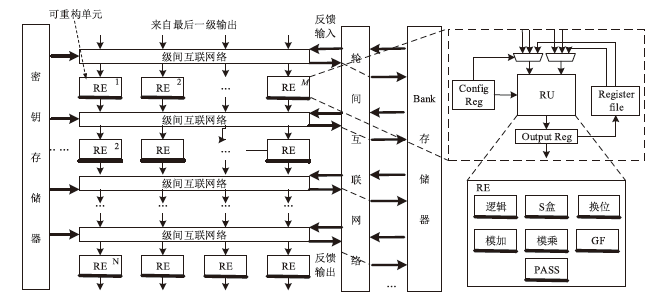

YUAN Hang. Research on Key Technologies of Dynamic Reconfigurable Cryptography Chip[D]. Beijing: Tsinghua University, 2019.

|

|

袁航. 动态可重构密码芯片关键技术研究[D]. 北京: 清华大学, 2019.

|

| [2] |

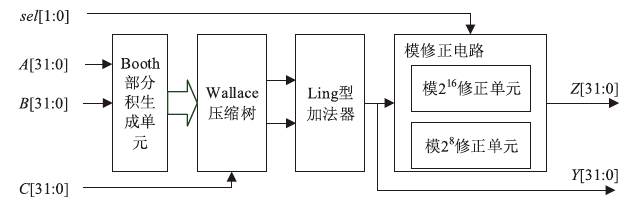

MENG Tao, DAI Zibin. Research on Reconfigurable Modulo Operation Unit[J]. Computer Engineering, 2008, 34(6): 145-147.

doi: 10.1108/EC-11-2015-0334

URL

|

|

孟涛, 戴紫彬. 可重构模运算单元的研究[J]. 计算机工程, 2008, 34(6): 145-147.

|

| [3] |

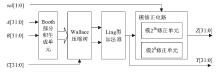

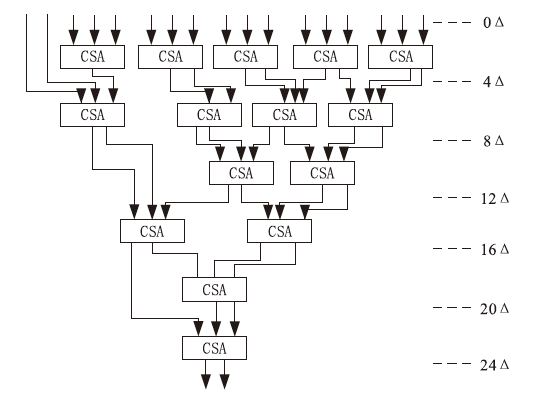

LI Wei, DAI Zibin, CHEN Tao. Low-Power 32-bit Multiplier Based on Leapfrog Wallace Tree[J]. Computer Engineering, 2008, 34(17): 229-231.

|

|

李伟, 戴紫彬, 陈韬. 基于跳跃式Wallace树的低功耗32位乘法器[J]. 计算机工程, 2008, 34(17): 229-231.

|

| [4] |

LI Wei, DAI Zibin, MENG Tao, et al. Design and Implementation of a High-Speed Reconfigurable Multiplier[EB/OL]. (2007-10-22)[2022-11-03]. https://ieeexplore.ieee.org/document/4415596.

|

| [5] |

JUANG T B, KUO C T, WU G L, et al. Multifunction RNS Modulo 2n ± 1 Multipliers[EB/OL]. (2021-09-06)[2022-11-03]. https://www.worldscientific.com/doi/abs/10.1142/S0218126612500272.

|

| [6] |

ZIMMERMANN R. Efficient VLSI Implementation of Modulo (2/Sup n//SPL Plusmn/1) Addition and Multiplication[EB/OL]. (1999-04-14)[2022-11-03]. https://ieeexplore.ieee.org/document/762841.

|

| [7] |

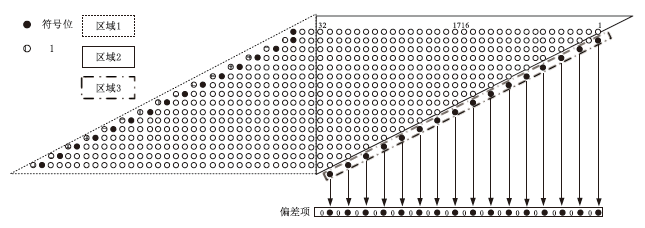

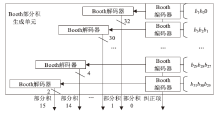

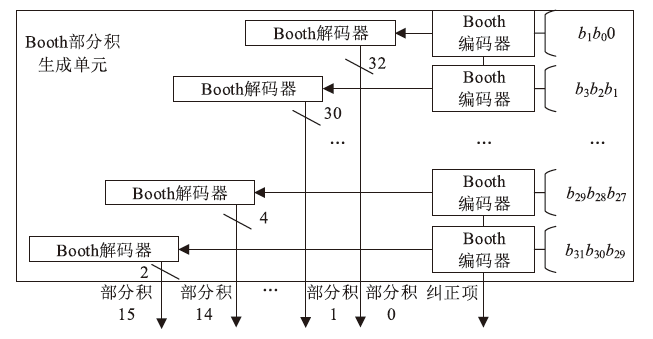

YAN Bin, LI Jun. Modulo 2n + 1 Multiplier Based on Radix-4 Booth Encoding[J]. Communications Technology, 2015, 48(10): 1168-1173.

|

|

鄢斌, 李军. 基于Radix-4 Booth编码的模2n+1乘法器设计[J]. 通信技术, 2015, 48(10): 1168-1173.

|

| [8] |

VASSALOS E, BAKALIS D, VERGOS H T. Configurable Booth-Encoded Modulo 2(exp n)± 1 Multipliers[EB/OL]. (2012-06-12)[2022-11-03]. https://ieeexplore.ieee.org/document/6226138?tp=&arnumber=6226138.

|

| [9] |

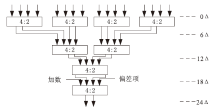

MURALIDHARAN R, CHANG C H. Radix-4 and Radix-8 Booth Encoded Multi-Modulus Multipliers[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2013, 60(11): 2940-2952.

doi: 10.1109/TCSI.2013.2252642

URL

|

| [10] |

CHENG Bin, WANG Dongyan, HAN Xiansheng, et al. Research of the Nature of Cyclic Shift XOR in Cryptography[J]. Cyber Security and Data Governance, 2011, 30(11): 79-80.

|

|

成彬, 王冬艳, 韩宪生, 等. 密码算法中的循环移位“异或”运算实质性研究[J]. 微型机与应用, 2011, 30(11): 79-80.

|

| [11] |

ZHANG Yan. Research and Design of RISC Architecture Specific Instruction Cryptographic Processor[D]. Zhengzhou: PLA Information Engineering University, 2008.

|

|

张琰. RISC结构专用指令密码处理器研究与设计[D]. 郑州: 解放军信息工程大学, 2008.

|

| [12] |

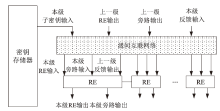

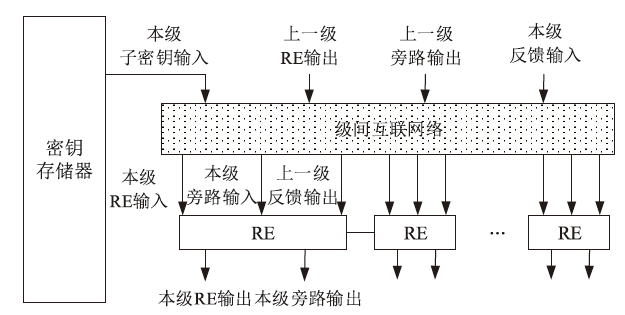

XUE Yuqian, DAI Zibin. Reconfiurable Multi-Launch Pipeline Processing Architecture for Block Cipher[J]. Application of Electronic Technique, 2020, 46(4): 40-44.

|

|

薛煜骞, 戴紫彬. 可重构分组密码多发射流水处理架构研究与设计[J]. 电子技术应用, 2020, 46(4): 40-44.

|

| [13] |

YEH W C, JEN C W. High-Speed Booth Encoded Parallel Multiplier Design[J]. IEEE Transactions on Computers, 2000, 49(7): 692-701.

doi: 10.1109/12.863039

URL

|

| [14] |

FRIED R. Minimizing Energy Dissipation in High-Speed Multipliers[C]// ACM. Proceedings of 1997 International Symposium on Low Power Electronics and Design. New York: ACM, 1997: 214-219.

|

| [15] |

ZHAO Zhongmin, LIN Zhenghao. Design of an Improved Wallace Tree Multiplier[J]. Electronic Design & Application World-Nikkei Electronics China, 2006(8): 113-116.

|

|

赵忠民, 林正浩. 一种改进的Wallace树型乘法器的设计[J]. 电子设计应用, 2006(8): 113-116.

|

| [16] |

KOREN I. Computer Arithmetic Algorithms[M]. Boston: Prentice-Hall, 1993.

|

| [17] |

CURIGER A V, BONNENBERG H, KAESLIN H. Regular VLSI Architectures for Multiplication Modulo (2/Sup n/+1)[J]. IEEE Journal of Solid-State Circuits, 1991, 26(7): 990-994.

doi: 10.1109/4.92018

URL

|

| [18] |

LAI Xuejia, MASSEY J L. A Proposal for a New Block Encryption Standard[C]// Springer. Advances in Cryptology-EUROCRYPT’90. Berlin:Springer, 2001: 389-404.

|

| [19] |

YANG Xiaohui. Research on Reconfigurable Design Technology for Block Cipher Processing[D]. Zhengzhou: PLA Information Engineering University, 2007.

|

|

杨晓辉. 面向分组密码处理的可重构设计技术研究[D]. 郑州: 解放军信息工程大学, 2007.

|

| [20] |

LI Jun, LYU Yongqi, Reconfigurable Design and Implementation of Modulo Multiplication[J]. Information Security And Communications Privacy, 2008(2): 97-99.

|

|

李军, 吕永其. 模2n±1乘法的可重构设计与实现[J]. 信息安全与通信保密, 2008(2): 97-99.

|

| [21] |

LI Xiaoquan. Optimization and Design of Reconfigurable Array Processing Unit for Group Encryption Algorithm[D]. Nanjing: Southeast University, 2016.

|

|

李小泉. 面向分组加密算法的可重构阵列处理单元优化与设计[D]. 南京: 东南大学, 2016.

|

), LIU Yanjiang, QU Tongzhou

), LIU Yanjiang, QU Tongzhou